= 20 and mine the

PHILIPIS.

USN Marks)

Marks) Hz and a of 5% is

Marks)

l class A 3 Marks) btain an 7 Marks) ero signal Determine 95 Marks)

ase shift n the R.C. 108 Marks) A colpitt's to have (66 Marks) | stability? (06 Marks)

of biasing (07 Marks) **d**culate the bias points (06 Marks) e diagram depletion ate source (07 Marks)

06ES33

## Third Semester B.E. Degree Examination, Dec.08/Jan.09 Logic Design

Time: 3 hrs.

Max. Marks: 100

Note:1. Answer any FIVE full questions, choosing at least two questions from each part A & B. 2. Missing data be suitably assumed.

## Part A

- Convert the given boolean function f(x,y,z) = [x + x z(y+z)] into maxterm canonical formula and hence highlight the importance of canonical formula.

- Distinguish the prime implicants and essential prime implicants. Determine the same of the function  $f(w,x,y,z) = \sum m(0,1,4,5,9,11,13,15)$  using K-map and hence the minimal sum (05 Marks) expression.

- c. Design a combinational logic circuit, which converts BCD code into Excess-3 code and (10 Marks) draw the circuit diagram.

- Using Quine-Mcluskey method and prime implicant reduction table, obtain the minimal sum 2 expression for the Boolean function  $f(w, x, y, z) = \sum_{i=1}^{n} m(1, 4, 6, 7, 8, 9, 10, 11, 15)$ .

- b. Obtain the minimal product of the following Boolean functions using VEM technique: (08 Marks)  $f(w,x,y,z) = \sum m(1,5,7,10,11) + dc(2,3,6,13)$

- Realize the following functions expressed in maxterm canonical form in two possible ways 3 using 3-8 line and decoder:

$$f_1(x_2, x_1, x_0) = \pi M(1, 2, 6, 7)$$

$f_2(x_2, x_1, x_0) = \pi M(1, 3, 6, 7)$

(10 Marks)

- What are the problems associated with the basic encoder? Explain, how can these problems (10 Marks) be overcome by priority encoder, considering 8 input lines.

- Implement the function  $f(w,x,y,z) = \sum m(0,1,5,6,7,9,10,15)$  using a 4:1 MUX with w, x as select lines:

- b. The 1-bit comparator had 3 outputs corresponding to x > y, x = y and x < y. It is possible to code these three outputs using two bits  $S_1S_0$  such as  $S_1$ ,  $S_0 = 00$ , 10, 01 for x = y, x > y and x < y respectively. This implies that only two-output lines occur from each 1-bit comparator. However at the output of the last 1-bit comparator, an additional network must be designed to convert the end results back to three outputs. Design such a 1-bit comparator (12 Marks) as well as the output converter network.

## Part B

- What is a Flip Flop? Discuss the working principle of SR Flip Flop with its truth table. Also 5 highlight the role of SR Flip Flop in switch debouncer circuit.

- With neat schematic diagram of master slave JK-FF, discuss its operation. Mention the (12 Marks) A ranges of JK-FF over master-slave SR-flip-flop.

shown in the table below 06 (a) Design a 4-bit universal shift register using positive edge triggered D flip-flops to operate as (12 Marks)

| Parallel load     | ኔ <del>፣</del>                          | <u>.                                    </u> | <u>د بر</u> |

|-------------------|-----------------------------------------|----------------------------------------------|-------------|

| Shift LEFT        | 12                                      | 0                                            |             |

| Shift RIGHT       | $\mathbf{I}_1$                          | -                                            | 0           |

| HOLD              | $I_0$                                   | 0                                            | 0           |

|                   |                                         | S                                            | So          |

| Register operatio | Data line selected   Register operation | Select line                                  | Selec       |

Table Q6 (a)

Ġ, edge triggered T-FF. Also draw the timing diagram. Explain the working principle of a mod-8 binary ripple counter, configured using positive (08 Marks)

Distinguish between Moore and Mealy model with necessary block diagrams. (08 Marks)

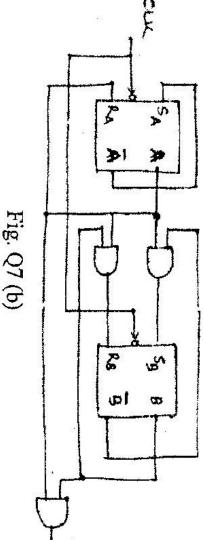

sequential circuit shown in figure Q7 (b) Give output function, excitation table and state transition diagram by analyzing the (12 Marks)

Construct Moore and Mealy state diagram that will detect input sequence 10110, when input pattern is detected, z is asserted high. Give state diagrams for each state (10 Marks)

Ġ diagram, transition table and excitation table. Design a cyclic mod 6 synchronous binary counter using JK flip-flop. Give the state (10 Marks)